子程新輝

ZICHENG ELECTRONIC

咨詢熱線:

服務熱線:

131-8386-5499

131-8386-5499

131-8386-5499

131-8386-5499

摘要:隨著物聯網的成熟和完善,無線通信技術和無線傳感網絡技術得到廣泛應用,由于通信頻率提升、電路復雜度增加等因素,設備的電磁兼容性成為必須考慮的問題。本篇文章分析了印制電路板(PCB)設計過程中電磁干擾(EMI)產生原因和相關抑制措施、解決方案,為相關電路設計工作提供參考和依據。

1 電磁兼容

由國標GB/T4365-1995定義,電磁兼容(Electromagnetic Compatibility)是指設備或系統再起電磁環境中能正常工作,且不對該環境中任何事物構成不能承受的電磁騷擾的能力,它主要包含兩方面的內容:電磁輻射和抗干擾能力。

電磁兼容(EMC)是保證信息系統裝備可靠和安全穩定的重要指標,也是裝備研制過程中必須解決的關鍵技術問題[1]。其性能是全球主要國家和地區電子和電氣產品必須獲得的各類安全認證之一[2]。根據IEC/CISPR國際標準,電磁兼容設計主要指電磁干擾(EMI)的抑制和防護。

2 PCB電磁干擾分析

印制電路板(PCB)是系統電路工作的平臺,其穩定性決定了電路工作的特性和穩定性。目前隨著消費電子、工業電子設計想著高速率、高集成度發展,據國際半導體技術發展藍圖預測,2022年芯片偏上時鐘頻率將提高至14.3GHz特征尺寸將發展到11.3mm,由于不斷升高的時鐘工作頻率、系統工作速度和電路集成度,PCB內部模塊信號串擾、外部電磁信號干擾成為影響系統穩定性、可靠性的制約因素。

其中產生電磁干擾成因主要分兩類:(1)PCB板布線間距小,信號線之間發生寄生耦合現象,進而產生干擾[3]。另外隨著高頻信號模塊的引入,走線之間不平衡而產生共模輻射同樣會產生干擾[4]。(2)由于布線過程中,PCB板出現的過孔、直角拐彎、鍵合線等情況,這些不連續結構導致信號產生串擾、反射,或引入噪聲。

此外,天線間、天線與其他電子設備間的相互干擾也更加復雜,并有可能影響天線和其他設備正常工作[5]。因此PCB的電磁兼容性分析和設計顯得尤為重要。

通過在PCB設計時期引入電磁兼容設計,通過軟件仿真對系統建模和分析,找到電磁干擾源,使仿真結果可視化,并做相關的EMC處理,以此降低系統電磁干擾。電磁兼容設計的介入時間越早,起花費成本就越低[6]。

3 物聯網系統PCB板電磁兼容設計方法

物聯網系統,根據業務速率不同,選用的通信模組有差異。對于高速業務普遍選用LTE CAT-4模組,中低速業務普遍選用CAT-1、eMTC模組,低速業務普遍選用NB-IoT模組。以上模組的信息傳輸速率已進入Gbps,并且系統時鐘頻率也再GHz范圍,因此需要將電路中的信號分布和電源分布考慮到該物聯網系統的PCB電磁兼容設計中去,進行EMC優化設計。

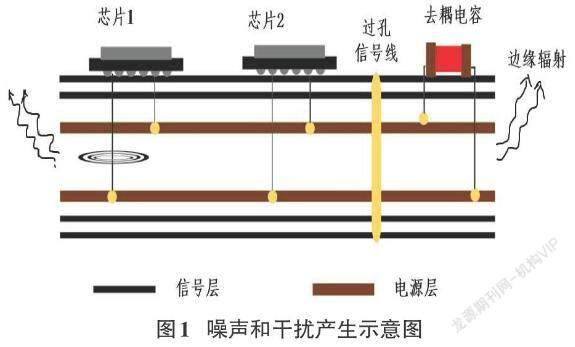

以下圖為例分析,芯片邏輯狀態的變化會造成瞬時電流,導致電壓波動,進而可能導致邏輯錯誤;另外,如果芯片1、2分別是數字芯片和模擬芯片,則數字芯片會產生同步切換噪聲影響模擬芯片;最后,信號線通過過孔穿過電源層時,同樣會帶來噪聲。可見,PCB電路中的噪聲是影響高速數字電路特性的主要原因之一[7]。

3.1 布局設計優化

(1)按系統功能及信號走向布局位置,物聯網通信模組和時鐘模塊屬于高速器件,應分開布局,防止模塊間干擾;屏蔽磁性元器件,CPU時鐘同敏感器件要保持一定的距離[8]。

(2)系統時鐘模塊靠近其相應的地線,形成有效回流。

(3)電源部分優化方案:為防止數字信號影響高頻模擬器件,將模擬電源和數字電源分開;為防止電源線產生尖峰電流,形成噪聲干擾,對于使用的電源類集成芯片安裝去耦電容(具體辦法參考3.3)。

(4)地線部分優化方案:地線和電源線之間加去耦電容(具體辦法參考3.3),抑制電源線上產生的輻射電流。